双极型集成电路,特别是像HFA16.0这类高速、高性能的型号,在现代电子系统中扮演着至关重要的角色,广泛应用于通信、医疗设备及高速数据采集等领域。这类集成电路由于其精细的半导体结构,对静电放电(ESD)事件极为敏感。ESD事件产生的瞬时高电压和大电流,极易造成器件内部PN结击穿、金属互连线熔断或栅氧层损伤,导致电路功能失效或性能永久性下降。因此,为HFA16.0这类双极型集成电路设计并实施有效的ESD保护,是确保其可靠性和长期稳定性的关键环节。

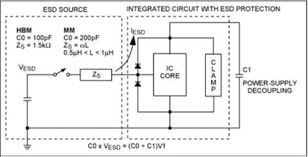

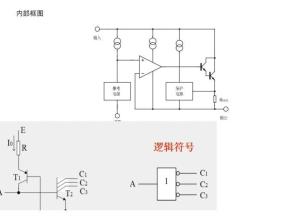

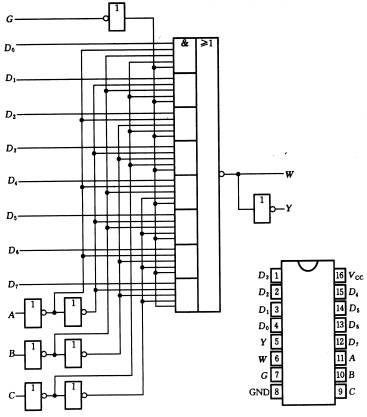

HFA16.0双极型集成电路的ESD保护设计,通常遵循“分级防护”和“片上集成”两大核心理念。在系统级,即在集成电路的输入端、输出端以及电源引脚与外部接口之间,会设置外部保护元件,如瞬态电压抑制二极管(TVS)、压敏电阻或专门的ESD保护芯片。这些元件构成了第一道防线,旨在将大部分ESD能量泄放至地,显著降低到达芯片引脚的过压幅度。也是更为核心的,是在芯片内部,即集成电路的版图设计层面,集成专门的片上ESD保护结构。对于双极型工艺,常用的片上保护结构包括但不限于:

- 钳位二极管结构:在信号引脚与电源轨(VCC/VEE)之间以及电源轨与地之间,设计正向或反向并联的二极管。当ESD事件发生时,二极管迅速导通,为电流提供一条低阻抗的泄放路径,将引脚电压钳制在安全范围内。

- 可控硅整流器(SCR)结构:SCR结构具有很高的电流泄放能力和较低的触发电压,单位面积下的ESD防护效能很高,非常适合用于需要高等级防护(如HBM模型要求较高)的引脚。

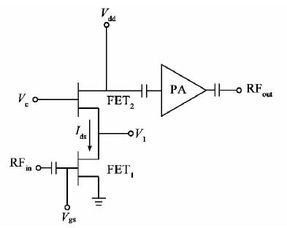

- 基于双极晶体管的保护电路:利用双极晶体管本身的特性,设计如栅接地(GG)或栅接电源(GD)配置的寄生双极晶体管路径,在ESD事件中被触发,以泄放电流。

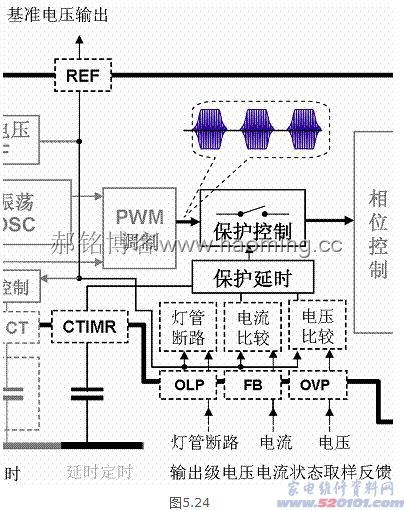

在设计HFA16.0的ESD保护时,必须进行细致的权衡。保护结构的引入必然会增加芯片的寄生电容(尤其是高速信号路径),这可能劣化HFA16.0的高频响应特性(如带宽、建立时间)。保护结构本身也会占用宝贵的芯片面积,增加制造成本。因此,设计工程师需要根据HFA16.0的具体应用场景(如工作频率、信号幅度)和ESD防护等级标准(如人体模型HBM、机器模型MM、带电器件模型CDM),通过仿真和测试,优化保护结构的尺寸、布局和触发特性,在确保足够的ESD鲁棒性与维持优异的电路性能之间找到最佳平衡点。

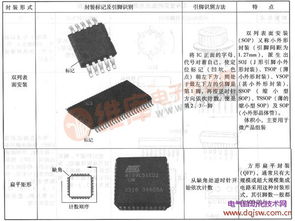

制造工艺和封装形式也对ESD防护能力有显著影响。先进的工艺控制可以减少缺陷,提高器件本身的一致性。而采用具有内部接地框架或屏蔽结构的封装,有助于减少外部ESD干扰耦合到芯片内部敏感节点。

为HFA16.0双极型集成电路提供可靠的ESD保护是一个涉及系统设计、芯片版图、工艺制造和封装测试的系统性工程。它要求设计者深入理解ESD的失效机理、双极型器件的物理特性以及电路的应用需求,通过多层次、协同优化的设计方案,才能最终交付一款既高速又坚固的集成电路产品,满足严苛的工业应用环境要求。